ASIC

Description

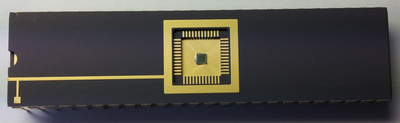

A complete cryptoprocessor for elliptic curve cryptography (ECC) has been designed during the PAVOIS project and implemented in 65nm CMOS technology (STMicroelectronics foundry via CMP services).

The implemented cryptoprocessor was designed for 256-bit prime finite fields elements and generic curves. It embeds: 1 multiplier, 1 adder and 1 inversion units for field-level computations. Various algorithms for scalar multiplication primitives can be programmed in software for curve-level computations. It was designed to evaluate algorithmic and arithmetic protections against side channel attacks (there is no hardware protection embedded in this ASIC version).

The circuit has been sent for fabrication to CMP services on June 20th, 2016 (the circuit was supposed to be sent for foundry in March 2016, but the run intially planed for March 7th, 2016 was cancelled by the foundry). After validation process at CMP, the circuit was sent for fabrication at STMicroelectronics foundry during several months. The produced chips were delivered on January 19th, 2016 (after several delays at foundry).

The test and evaluation of the circuits will be performed in the next months (as soon as we find support and time since PAVOIS is already finished).